CMSC 512 Homework 4

There is document - CMSC 512 Homework 4 available here for reading and downloading. Use the download button below or simple online reader.

The file extension - PDF and ranks to the School Work category.

Tags

Related

Comments

Log in to leave a message!

Description

Download CMSC 512 Homework 4

Transcripts

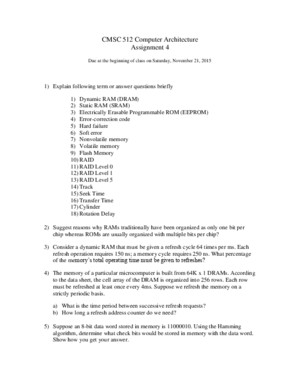

CMSC 512 Computer Architecture Assignment 4 Due at the beginning of class on Saturday, November 21, 2015 1) Explain following term or answer questions briefly 1) Dynamic RAM (DRAM) 2) Static RAM (SRAM) 3) Electrically Erasable Programmable ROM (EEPROM) 4) Error-correction code 5) Hard failure 6) Soft error 7) Nonvolatile memory 8) Volatile memory 9) Flash Memory 10) RAID 11) RAID Level 0 12) RAID Level 1 13) RAID Level 5 14) Track 15) Seek Time 16) Transfer Time 17) Cylinder 18) Rotation Delay 2) Suggest reasons why RAMs traditionally have been organized as only one bit per chip whereas ROMs are usually organized with multiple bits per chip? 3) Consider a dynamic RAM that must be given a refresh cycle 64 times per ms Each refresh operation requires 150 ns; a memory cycle requires 250 ns What percentage of the me mory’s total operating time must be given to refreshes? 4) The memory of a particular microcomputer is built from 64K x 1 DRAMs According to the data sheet, the cell array of the DRAM is organized into 256 rows Each row must be refreshed at least once every 4ms Suppose we refresh the memory on a strictly periodic basis a) What is the time period between successive refresh requests? b) How long a refresh address counter do we need? 5) Suppose an 8-bit data word stored in memory is 11000010 Using the Hamming algorithm, determine what check bits would be stored in memory with the data word Show how you get your answer 6) How many check bits are needed if the Hamming error correction code is used to detect single bit errors in a 1024-bit data word? 7) Consider a 4-drive, 200GB-per-drive RAID array What is the available data storage capacity for each of the RAID levels, 0, 1, 2, 3, 4, 5 and 6? 8) Consider a disk with a sector size of 512 bytes, 2000 tracks per surface,50 sectors per track, five double-sided platters, and average seek time of 10 msec a) What is the capacity of a track in bytes? What is the capacity of each surface? What is the capacity of the disk? b) How many cylinders does the disk have? c) Give examples of valid block sizes Is 256 bytes a valid block size? 2048? 51200? d) If the disk platters rotate at 5400 rpm (revolutions per minute), what is the maximum rotational delay? e) If one track of data can be transferred per revolution, what is the transfer rate?

Recommended